SNVS988B-JULY 2013-REVISED APRIL 2018

LMZ35003

# LMZ35003 2.5-A Power Module With 7V-50V Input in QFN Package

#### **Features**

- Complete Integrated Power Solution Allows Small Footprint, Low-Profile Design

- Wide Input Voltage Range from 7 V to 50 V

- Output Adjustable from 2.5 V to 15 V

- 65-V Surge Capability

- Efficiencies Up To 96%

- Adjustable Switching Frequency (300 kHz to 1 MHz)

- Synchronizes to an External Clock

- Adjustable Slow-Start

- Output Voltage Sequencing and Tracking

- Power Good Output

- Programmable Undervoltage Lockout (UVLO)

- **Output Overcurrent Protection**

- Over Temperature Protection

- Pre-bias Output Start-up

- Operating Temperature Range: -40°C to 85°C

- Enhanced Thermal Performance: 14°C/W

- Meets EN55022 Class B Emissions Integrated Shielded Inductor

- For Design Help visit http://www.ti.com/LMZ35003

- Create a Custom Design Using the LMZ35003 With the WEBENCH® Power Designer

# Applications

- Industrial and Motor Controls

- **Automated Test Equipment**

- Medical and Imaging Equipment

- High Density Power Systems

# 3 Description

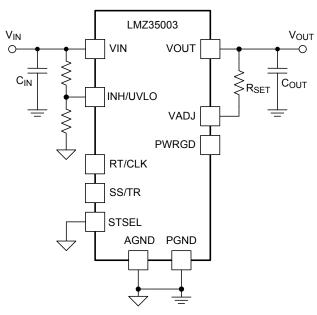

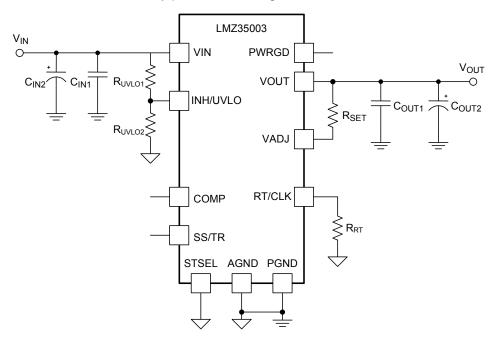

The LMZ35003 power module is an easy-to-use integrated power solution that combines a 2.5-A DC/DC converter with a shielded inductor and passives into a low profile, QFN package. This total power solution allows as few as five external components and eliminates the loop compensation and magnetics part selection process.

The small 9 mm × 11 mm × 2.8 mm, QFN package is easy to solder onto a printed circuit board and allows a compact point-of-load design with greater than 90% efficiency and excellent power dissipation capability. The LMZ35003 offers the flexibility and the featureset of a discrete point-of-load design and is ideal for powering a wide range of ICs and systems. Advanced packaging technology affords a robust and reliable power solution compatible with standard QFN mounting and testing techniques.

### Simplified Application

### **Table 1. Ordering Information**

For the most current package and ordering information, see the Package Option Addendum at the end of this datasheet, or see the TI website at www.ti.com.

### 4 Specifications

# 4.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating temperature range (unless otherwise noted)

|                                                | (4                                                                                                                                            | MIN  | MAX                | UNIT |  |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|--|

|                                                | VIN                                                                                                                                           | -0.3 | 65                 | V    |  |

|                                                | INH/UVLO                                                                                                                                      | -0.3 | 5                  | V    |  |

|                                                | VADJ                                                                                                                                          | -0.3 | 3                  | V    |  |

| Input Voltage                                  | PWRGD                                                                                                                                         | -0.3 | 6                  | V    |  |

|                                                | SS/TR                                                                                                                                         | -0.3 | 3                  | V    |  |

|                                                | STSEL                                                                                                                                         | -0.3 | 3                  | V    |  |

|                                                | RT/CLK                                                                                                                                        | -0.3 | 3.6                | V    |  |

|                                                | PH                                                                                                                                            | -0.6 | 65                 | V    |  |

| Output Voltage                                 | PH 10ns Transient                                                                                                                             | -2   | 65                 | V    |  |

|                                                | VOUT                                                                                                                                          | -0.6 | VIN                | V    |  |

| V <sub>DIFF</sub> (GND to exposed thermal pad) |                                                                                                                                               |      | ±200               | mV   |  |

| 0                                              | RT/CLK                                                                                                                                        |      | 100                | μA   |  |

| Source Current                                 | INH/UVLO                                                                                                                                      |      | 100                | μA   |  |

| Cials Company                                  | SS/TRK                                                                                                                                        |      | 200                | μA   |  |

| Sink Current                                   | PWRGD                                                                                                                                         |      | 10                 | mA   |  |

| Operating Junction Temperature                 |                                                                                                                                               | -40  | 105 <sup>(2)</sup> | °C   |  |

| Storage Temperature                            |                                                                                                                                               | -65  | 150                | °C   |  |

| Peak Reflow Case Temperature (3)               |                                                                                                                                               |      | 250 <sup>(4)</sup> | °C   |  |

| Maximum Number of Reflows Allow                | ed <sup>(3)</sup>                                                                                                                             |      | 3 <sup>(4)</sup>   |      |  |

| Mechanical Shock                               | Mil-STD-883D, Method 2002.3, 1 msec, 1/2 sine, mounted                                                                                        |      | 1500               | G    |  |

| Mechanical Vibration                           | #200  RT/CLK 100 INH/UVLO 100 SS/TRK 200 PWRGD 10  -40 105 <sup>(2)</sup> -65 150  3) 250 <sup>(4)</sup> owed <sup>(3)</sup> 3 <sup>(4)</sup> |      |                    |      |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 4.2 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                               | MIN | MAX  | UNIT |

|------------------|-------------------------------|-----|------|------|

| V <sub>IN</sub>  | Input Voltage                 | 7   | 50   | V    |

| V <sub>OUT</sub> | Output Voltage                | 2.5 | 15   | V    |

| f <sub>SW</sub>  | Switching Frequency           | 400 | 1000 | kHz  |

| T <sub>A</sub>   | Operating Ambient Temperature | -40 | 85   | °C   |

<sup>(2)</sup> See the temperature derating curves in the Typical Characteristics section for thermal information.

<sup>(3)</sup> For soldering specifications, refer to the Soldering Requirements for BQFN Packages application note.

<sup>(4)</sup> Devices with a date code prior to week 14 2018 (1814) have a peak reflow case temperature of 240°C with a maximum of one reflow.

#### 4.3 Thermal Information

|               |                                                           | LMZ35003 |      |

|---------------|-----------------------------------------------------------|----------|------|

|               | THERMAL METRIC <sup>(1)</sup>                             | RKG      | UNIT |

|               |                                                           | 41 PINS  |      |

| $\theta_{JA}$ | Junction-to-ambient thermal resistance (2)                | 14       |      |

| ΨЈТ           | Junction-to-top characterization parameter <sup>(3)</sup> | 3.3      | °C/W |

| ΨЈВ           | Junction-to-board characterization parameter (4)          | 6.8      |      |

- (1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics (SPRA953)

- The junction-to-ambient thermal resistance,  $\theta_{JA}$ , applies to devices soldered directly to a 100 mm x 100 mm double-sided, 4-layer PCB with 1 oz. copper and natural convection cooling. Additional airflow reduces  $\theta_{JA}$ .

- (3) The junction-to-top characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature, T<sub>J</sub>, of a device in a real system, using a procedure described in JESD51-2A (sections 6 and 7).  $T_J = \psi_{JT}$  \* Pdis +  $T_T$ , where Pdis is the power dissipated in the device and  $T_T$  is the temperature of the top of the device.

- The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature,  $T_{J}$ , of a device in a real system, using a procedure described in JESD51-2A (sections 6 and 7).  $T_{J} = \psi_{JB}$  \* Pdis +  $T_{B}$ ; where Pdis is the power dissipated in the device and  $T_{B}$  is the temperature of the board 1mm from the device.

#### 4.4 Package Specifications

|                             | LMZ35003                                                              | UNIT      |

|-----------------------------|-----------------------------------------------------------------------|-----------|

| Weight                      |                                                                       | 0.9 grams |

| Flammability                | Meets UL 94 V-O                                                       |           |

| MTBF Calculated reliability | Per Bellcore TR-332, 50% stress, T <sub>A</sub> = 40°C, ground benign | 31.7 MHrs |

## 4.5 Electrical Characteristics

-40°C ≤  $T_A$  ≤ +85°C,  $V_{IN}$  = 24 V,  $V_{OUT}$  = 5.0 V,  $I_{OUT}$  = 2.5 A,  $R_T$  = Open  $C_{IN}$  = 2 x 2.2  $\mu$ F ceramic,  $C_{OUT}$  = 2 x 47  $\mu$ F ceramic (unless otherwise noted)

|                       | PARAMETER                      |                                                   | TEST CONDITIONS                                     |                                   | MIN                  | TYP               | MAX                  | UNIT             |

|-----------------------|--------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------------|----------------------|-------------------|----------------------|------------------|

| I <sub>OUT</sub>      | Output current                 | Over input voltage an                             | d output voltage range                              | )                                 | 0                    |                   | 2.5                  | Α                |

| V <sub>IN</sub>       | Input voltage range            | Over output current ra                            | ange                                                |                                   | 7.0 <sup>(1)</sup>   |                   | 50 <sup>(2)</sup>    | V                |

| UVLO                  | VIN Undervoltage lockout       | No hysteresis, Rising                             | and Falling                                         |                                   |                      | 2.5               |                      | V                |

| V <sub>OUT(adj)</sub> | Output voltage adjust range    | Over output current ra                            | ange                                                |                                   | 2.5 <sup>(3)</sup>   |                   | 15                   | V                |

|                       | Set-point voltage tolerance    | $T_A = 25^{\circ}C; I_{OUT} = 100$                | ) mA                                                |                                   |                      |                   | ±2.0% <sup>(4)</sup> |                  |

|                       | Temperature variation          | -40°C ≤ T <sub>A</sub> ≤ +85°C                    |                                                     |                                   |                      | ±0.5%             | ±1.0%                |                  |

| V <sub>OUT</sub>      | Line regulation                | Over input voltage ra                             | nge                                                 |                                   |                      | ±0.1%             |                      |                  |

| Load regulation       | Over output current range      |                                                   |                                                     |                                   | ±0.4%                |                   |                      |                  |

|                       | Total output voltage variation | Includes set-point, lin                           |                                                     |                                   | ±3.0% <sup>(4)</sup> |                   |                      |                  |

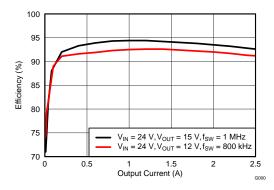

|                       |                                |                                                   | V <sub>OUT</sub>                                    | = 12 V, f <sub>SW</sub> = 800 kHz |                      | 93 %              |                      |                  |

|                       |                                | $V_{IN} = 24 \text{ V}$ $I_{OUT} = 1.5 \text{ A}$ | $V_{OUT} = 5.0 \text{ V}, f_{SW} = 500 \text{ kHz}$ |                                   |                      | 84 %              |                      |                  |

|                       | <b>F#</b> :-:                  |                                                   | $V_{OUT} = 3.3 \text{ V}, f_{SW} = 400 \text{ kHz}$ |                                   |                      | 79 %              |                      |                  |

| η                     | Efficiency                     | V <sub>IN</sub> = 48 V                            | V <sub>OUT</sub> = 12 V, f <sub>SW</sub> = 800 kHz  |                                   |                      | 87 %              |                      |                  |

|                       |                                | I <sub>OUT</sub> = 1.5 A                          | V <sub>OUT</sub> = 5.0 V, f <sub>SW</sub> = 500 kHz |                                   |                      | 79 %              |                      |                  |

|                       |                                |                                                   | V <sub>OUT</sub> :                                  |                                   | 74 %                 |                   |                      |                  |

|                       | Output voltage ripple          | 20 MHz bandwith, 0.2                              | 25 A ≤ I <sub>OUT</sub> ≤ 2.5 A, VC                 | OUT ≥ 3.3V                        |                      | 1% <sup>(3)</sup> |                      | V <sub>OUT</sub> |

| I <sub>LIM</sub>      | Current limit threshold        |                                                   |                                                     |                                   |                      | 5.1               |                      | Α                |

|                       |                                | 4.0.0/                                            | 50 t- 4000/                                         | Recovery time                     |                      | 400               |                      | μs               |

|                       | Transient response             | OUT(max)                                          |                                                     | VOUT over/undershoot              |                      | 90                |                      | mV               |

| V <sub>INH</sub>      | Inhibit threshold voltage      | No hysteresis                                     |                                                     |                                   | 1.15                 | 1.25              | 1.36 (5)             | V                |

<sup>(1)</sup> For output voltages ≤ 12 V, the minimum input voltage is 7 V or (V<sub>OUT</sub>+ 3 V), whichever is greater. For output voltages > 12 V, the minimum input voltage is (1.33 x  $V_{OUT}$ ). See Figure 27 for more details. The maximum input voltage is 50 V or (15 x  $V_{OUT}$ ), whichever is less.

Value when no voltage divider is present at the INH/UVLO pin.

Output voltages < 3.3 V are subject to reduced  $V_{\text{IN}(\text{max})}$  specifications and higher ripple magnitudes. The stated limit of the set-point voltage tolerance includes the tolerance of both the internal voltage reference and the internal adjustment resistor. The overall output voltage tolerance is affected by the tolerance of the external R<sub>SET</sub> resistor.

# **Electrical Characteristics (continued)**

-40°C ≤  $T_A$  ≤ +85°C,  $V_{IN}$  = 24 V,  $V_{OUT}$  = 5.0 V,  $I_{OUT}$  = 2.5 A,  $R_T$  = Open  $C_{IN}$  = 2 x 2.2  $\mu$ F ceramic,  $C_{OUT}$  = 2 x 47  $\mu$ F ceramic (unless otherwise noted)

|                             | PARAMETER                    | TEST CONDITION               | S           | MIN     | TYP  | MAX  | UNIT |

|-----------------------------|------------------------------|------------------------------|-------------|---------|------|------|------|

|                             | INII I Innut ourrent         | V <sub>INH</sub> < 1.15 V    |             |         | -0.9 |      | μА   |

| I <sub>INH</sub>            | INH Input current            | V <sub>INH</sub> > 1.36 V    |             |         | -3.8 |      | μА   |

| I <sub>I(stby)</sub>        | Input standby current        | INH pin to AGND              |             |         | 1.3  | 4    | μΑ   |

|                             |                              | V vision                     | Good        |         | 94%  |      |      |

|                             | DWDCD Throubalds             | V <sub>OUT</sub> rising Faul |             |         | 109% |      |      |

| PWRGD Thresholds Power Good | PWRGD Thresholds             | V folling                    | Fault       |         | 91%  |      |      |

|                             |                              | V <sub>OUT</sub> falling     | Good        |         | 106% |      |      |

|                             | PWRGD Low Voltage            | I(PWRGD) = 3.5 mA            |             | 0.2     |      | V    |      |

| f <sub>SW</sub>             | Switching frequency          | RT/CLK pin OPEN              |             | 300     | 400  | 500  | kHz  |

| f <sub>CLK</sub>            | Synchronization frequency    |                              |             | 300     |      | 1000 | kHz  |

| V <sub>CLK-H</sub>          | CLK High-Level Threshold     | CLK Control                  |             |         | 1.9  | 2.2  | V    |

| V <sub>CLK-L</sub>          | CLK Low-Level Threshold      | CLK Control                  |             | 0.5     | 0.7  |      | V    |

| D <sub>CLK</sub>            | CLK Duty cycle               |                              |             | 25%     | 50%  | 75%  |      |

|                             | The second Chartelesses      | Thermal shutdown             |             |         | 180  |      | °C   |

|                             | Thermal Shutdown             | Thermal shutdown hysteresis  |             |         | 15   |      | °C   |

| 0                           | Future line at annual trans- |                              | Ceramic     | 4.4 (6) | 10   |      |      |

| C <sub>IN</sub>             | External input capacitance   |                              | Non-ceramic |         | 22   |      | μF   |

| C <sub>OUT</sub>            | External output capacitance  |                              |             | 100 (7) |      | 430  | μF   |

<sup>(6)</sup> A minimum of 4.4µF of ceramic external capacitance is required across the input (VIN and PGND connected) for proper operation. Locate the capacitor close to the device. See Table 3 for more details.

<sup>(7)</sup> The required capacitance must include at least 2 x 47μF ceramic capacitors (or 4 x 22μF). Locate the capacitance close to the device. Adding additional capacitance close to the load improves the response of the regulator to load transients. See Table 3 for more details.

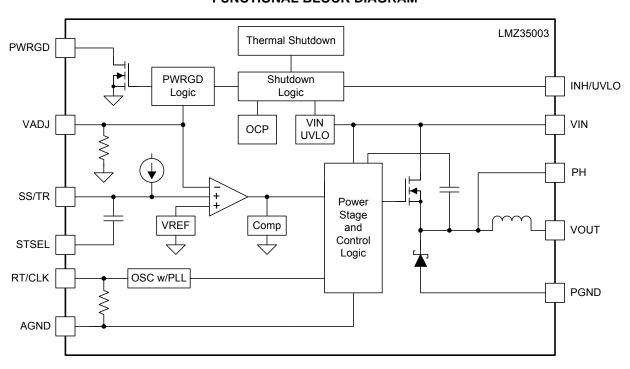

# 5 Device Information

### **FUNCTIONAL BLOCK DIAGRAM**

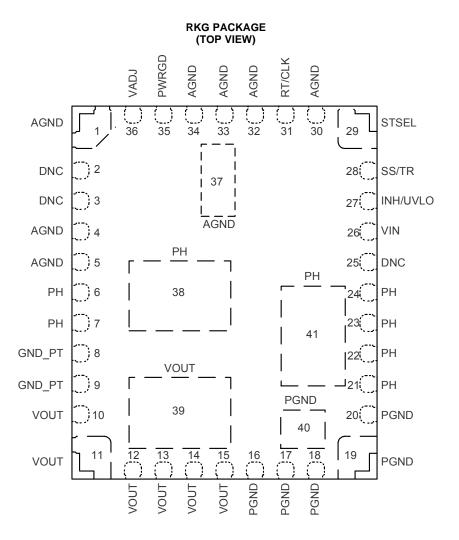

### **Table 2. PIN DESCRIPTIONS**

| TER      | MINAL | DESCRIPTION                                                                                                                                                                                                                                                       |

|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.   | DESCRIPTION                                                                                                                                                                                                                                                       |

|          | 1     |                                                                                                                                                                                                                                                                   |

|          | 4     |                                                                                                                                                                                                                                                                   |

|          | 5     | These pins are connected to the internal analog ground (AGND) of the device. This node should be treated                                                                                                                                                          |

| AGND     | 30    | as the zero volt ground reference for the analog control circuitry. Pad 37 should be connected to PCB ground planes using multiple vias for good thermal performance. Not all pins are connected together                                                         |

| AGND     | 32    | internally. All pins must be connected together externally with a copper plane or pour directly under the                                                                                                                                                         |

|          | 33    | module. Connect AGND to PGND at a single point (GND_PT; pins 8 & 9). See Layout Recommendations.                                                                                                                                                                  |

|          | 34    |                                                                                                                                                                                                                                                                   |

|          | 37    |                                                                                                                                                                                                                                                                   |

|          | 2     |                                                                                                                                                                                                                                                                   |

| DNC      | 3     | Do Not Connect. Do not connect these pins to AGND, to another DNC pin, or to any other voltage. These pins are connected to internal circuitry. Each pin must be soldered to an isolated pad.                                                                     |

|          | 25    | pins are connected to internal circuitry. Each pin must be soldered to an isolated pad.                                                                                                                                                                           |

|          | 6     |                                                                                                                                                                                                                                                                   |

|          | 7     |                                                                                                                                                                                                                                                                   |

|          | 21    |                                                                                                                                                                                                                                                                   |

|          | 22    | Phase switch node. Do not place any external component on these pins or tie them to a pin of another                                                                                                                                                              |

| PH       | 23    | function.                                                                                                                                                                                                                                                         |

|          | 24    |                                                                                                                                                                                                                                                                   |

|          | 38    |                                                                                                                                                                                                                                                                   |

|          | 41    |                                                                                                                                                                                                                                                                   |

|          | 8     | Ground Point. Connect AGND to PGND at these pins as shown in the Layout Considerations. These pins                                                                                                                                                                |

| GND_PT   | 9     | are not connected to internal circuitry, and are not connected to one other.                                                                                                                                                                                      |

|          | 10    |                                                                                                                                                                                                                                                                   |

|          | 11    |                                                                                                                                                                                                                                                                   |

|          | 12    |                                                                                                                                                                                                                                                                   |

| VOUT     | 13    | Output voltage. These pins are connected to the internal output inductor. Connect these pins to the output load and connect external bypass capacitors between these pins and PGND. Connect a resistor from these                                                 |

|          | 14    | pins to VADJ to set the output voltage.                                                                                                                                                                                                                           |

|          | 15    |                                                                                                                                                                                                                                                                   |

|          | 39    |                                                                                                                                                                                                                                                                   |

|          | 16    |                                                                                                                                                                                                                                                                   |

|          | 17    |                                                                                                                                                                                                                                                                   |

|          | 18    | This is the return current path for the power stage of the device. Connect these pins to the load and to the                                                                                                                                                      |

| PGND     | 19    | bypass capacitors associated with VIN and VOUT. Pad 40 should be connected to PCB ground planes using                                                                                                                                                             |

|          | 20    | multiple vias for good thermal performance.                                                                                                                                                                                                                       |

|          | 40    |                                                                                                                                                                                                                                                                   |

| VIN      | 26    | Input voltage. This pin supplies all power to the converter. Connect this pin to the input supply and connect bypass capacitors between this pin and PGND.                                                                                                        |

| INH/UVLO | 27    | Inhibit and UVLO adjust pin. Use an open drain or open collector logic device to ground this pin to control the INH function. A resistor divider between this pin, AGND, and VIN sets the UVLO voltage.                                                           |

| SS/TR    | 28    | Slow-start and tracking pin. Connecting an external capacitor to this pin adjusts the output voltage rise time. A voltage applied to this pin allows for tracking and sequencing control.                                                                         |

| STSEL    | 29    | Slow-start or track feature select. Connect this pin to AGND to enable the internal SS capacitor. Leave this pin open to enable the TR feature.                                                                                                                   |

| RT/CLK   | 31    | This pin is connected to an internal frequency setting resistor which sets the default switching frequency. An external resistor can be connected from this pin to AGND to increase the frequency. This pin can also be used to synchronize to an external clock. |

| PWRGD    | 35    | Power Good flag pin. This open drain output asserts low if the output voltage is more than approximately ±6% out of regulation. A pull-up resistor is required.                                                                                                   |

| VADJ     | 36    | Connecting a resistor between this pin and VOUT sets the output voltage.                                                                                                                                                                                          |

Submit Documentation Feedback

Copyright © 2013–2018, Texas Instruments Incorporated

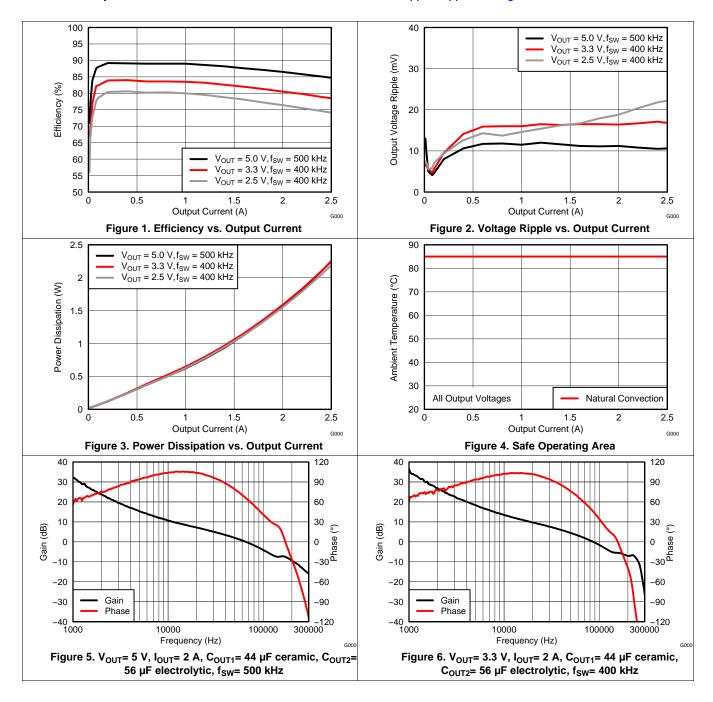

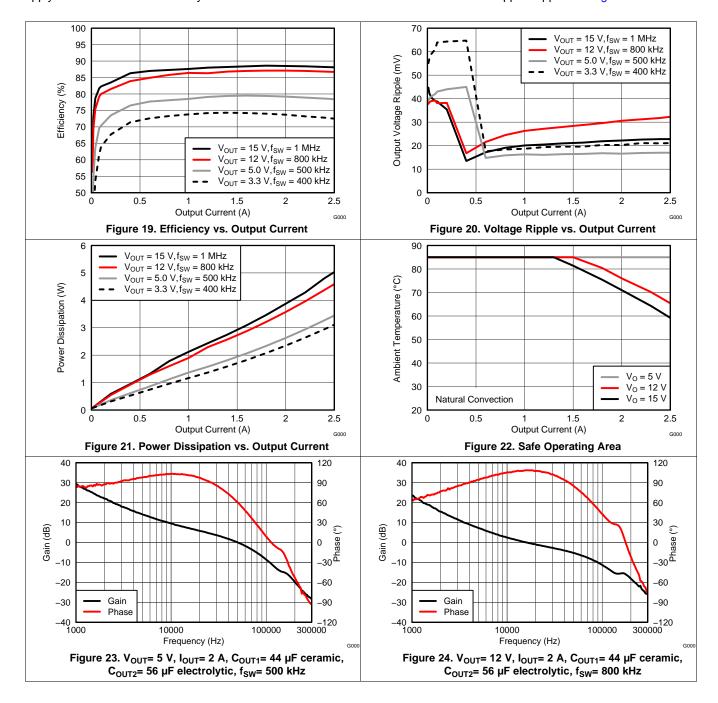

# 6 Typical Characteristics (VIN = 12 V)

The electrical characteristic data has been developed from actual products tested at  $25^{\circ}$ C. This data is considered typical for the converter. Applies to Figure 1, Figure 2, and Figure 3. The temperature derating curves represent the conditions at which internal components are at or below the manufacturer's maximum operating temperatures. Derating limits apply to devices soldered directly to a  $100 \text{ mm} \times 100 \text{ mm}$  double-sided PCB with 1 oz. copper. Applies to Figure 4.

Submit Documentation Feedback

Copyright © 2013–2018, Texas Instruments Incorporated

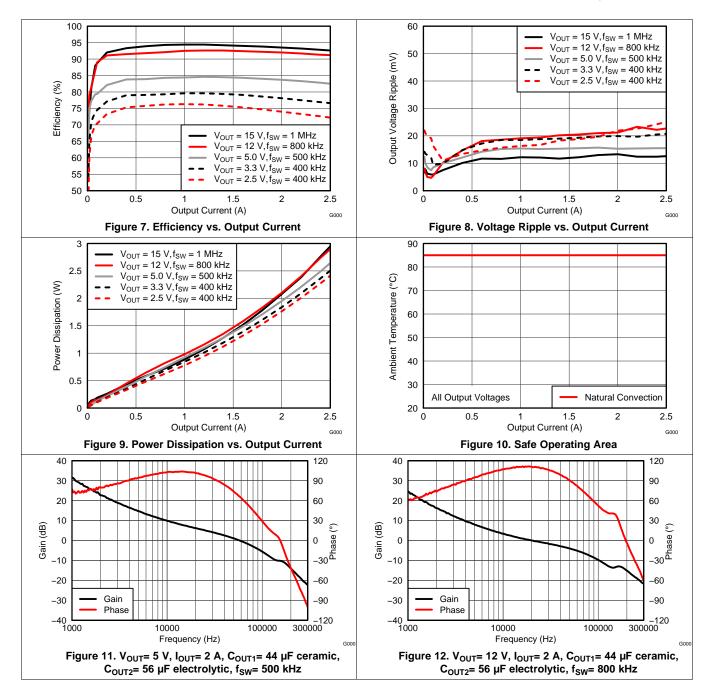

# 7 Typical Characteristics (VIN = 24 V)

The electrical characteristic data has been developed from actual products tested at 25°C. This data is considered typical for the converter. Applies to Figure 7, Figure 8, and Figure 9. At light load the output voltage ripple may increase due to pulse skipping. See Light-Load Behavior for more information. Applies to Figure 8. The temperature derating curves represent the conditions at which internal components are at or below the manufacturer's maximum operating temperatures. Derating limits apply to devices soldered directly to a 100 mm × 100 mm double-sided PCB with 1 oz. copper. Applies to Figure 10.

Copyright © 2013–2018, Texas Instruments Incorporated

Submit Documentation Feedback

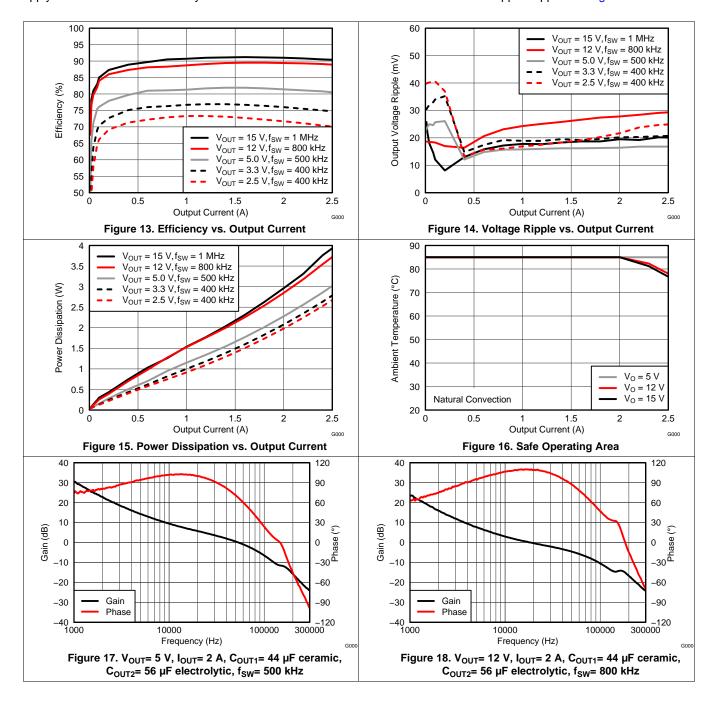

# 8 Typical Characteristics (VIN = 36 V)

The electrical characteristic data has been developed from actual products tested at 25°C. This data is considered typical for the converter. Applies to Figure 13, Figure 14, and Figure 15. At light load the output voltage ripple may increase due to pulse skipping. See Light-Load Behavior for more information. Applies to Figure 14. The temperature derating curves represent the conditions at which internal components are at or below the manufacturer's maximum operating temperatures. Derating limits apply to devices soldered directly to a 100 mm × 100 mm double-sided PCB with 1 oz. copper. Applies to Figure 16.

Submit Documentation Feedback

Copyright © 2013–2018, Texas Instruments Incorporated

# 9 Typical Characteristics (VIN = 48 V)

The electrical characteristic data has been developed from actual products tested at 25°C. This data is considered typical for the converter. Applies to Figure 19, Figure 20, and Figure 21. At light load the output voltage ripple may increase due to pulse skipping. See Light-Load Behavior for more information. Applies to Figure 20. The temperature derating curves represent the conditions at which internal components are at or below the manufacturer's maximum operating temperatures. Derating limits apply to devices soldered directly to a 100 mm × 100 mm double-sided PCB with 1 oz. copper. Applies to Figure 22.

Copyright © 2013–2018, Texas Instruments Incorporated

Submit Documentation Feedback

# 10 Capacitor Recommendations for the LMZ35003 Power Supply

### 10.1 Capacitor Technologies

### 10.1.1 Electrolytic, Polymer-Electrolytic Capacitors

When using electrolytic capacitors, high-quality, computer-grade electrolytic capacitors are recommended. Polymer-electrolytic type capacitors are recommended for applications where the ambient operating temperature is less than 0°C. The Sanyo OS-CON capacitor series is suggested due to the lower ESR, higher rated surge, power dissipation, ripple current capability, and small package size. Aluminum electrolytic capacitors provide adequate decoupling over the frequency range of 2 kHz to 150 kHz, and are suitable when ambient temperatures are above 0°C.

#### 10.1.2 Ceramic Capacitors

The performance of aluminum electrolytic capacitors is less effective than ceramic capacitors above 150 kHz. Multilayer ceramic capacitors have a low ESR and a resonant frequency higher than the bandwidth of the regulator. They can be used to reduce the reflected ripple current at the input as well as improve the transient response of the output.

#### 10.1.3 Tantalum, Polymer-Tantalum Capacitors

Polymer-tantalum type capacitors are recommended for applications where the ambient operating temperature is less than 0°C. The Sanyo POSCAP series and Kemet T530 capacitor series are recommended rather than many other tantalum types due to their lower ESR, higher rated surge, power dissipation, ripple current capability, and small package size. Tantalum capacitors that have no stated ESR or surge current rating are not recommended for power applications.

### 10.2 Input Capacitor

The LMZ35003 requires a minimum input capacitance of 4.4  $\mu$ F of ceramic type. The voltage rating of input capacitors must be greater than the maximum input voltage. The ripple current rating of the capacitor must be at least 450 mArms. Table 3 includes a preferred list of capacitors by vendor.

#### 10.3 Output Capacitor

The output capacitance of the LMZ35003 can be comprised of either all ceramic capacitors, or a combination of ceramic and bulk capacitors. The required output capacitance must include at least 100  $\mu$ F of ceramic type (or 2 x 47  $\mu$ F). When adding additional non-ceramic bulk capacitors, low-ESR devices like the ones recommended in Table 3 are required. Additional capacitance above the minimum is determined by actual transient deviation requirements. Table 3 includes a preferred list of capacitors by vendor.

Table 3. Recommended Input/Output Capacitors (1)

|        |        |                    | CAP                       | CAPACITOR CHARACTERISTICS |                            |  |  |  |

|--------|--------|--------------------|---------------------------|---------------------------|----------------------------|--|--|--|

| VENDOR | SERIES | PART NUMBER        | WORKING<br>VOLTAGE<br>(V) | CAPACITANCE<br>(µF)       | ESR <sup>(2)</sup><br>(mΩ) |  |  |  |

| Murata | X5R    | GRM31CR61H225KA88L | 50                        | 4.7                       | 2                          |  |  |  |

| TDK    | X5R    | C3216X5R1H475K     | 50                        | 4.7                       | 2                          |  |  |  |

| Murata | X5R    | GRM32ER61E226K     | 16                        | 22                        | 2                          |  |  |  |

| TDK    | X5R    | C3225X5R0J476K     | 6.3                       | 47                        | 2                          |  |  |  |

| Murata | X5R    | GRM32ER60J476M     | 6.3                       | 47                        | 2                          |  |  |  |

| Sanyo  | POSCAP | 16TQC68M           | 16                        | 68                        | 50                         |  |  |  |

| Sanyo  | POSCAP | 6TPE100MI          | 6.3                       | 100                       | 25                         |  |  |  |

| Kemet  | T530   | T530D227M006ATE006 | 6.3                       | 220                       | 6                          |  |  |  |

<sup>(1)</sup> Capacitor Supplier Verification, RoHS, Lead-free and Material Details

Consult capacitor suppliers regarding availability, material composition, RoHS and lead-free status, and manufacturing process requirements for any capacitors identified in this table.

<sup>(2)</sup> Maximum ESR @ 100 kHz, 25°C.

### 11 Application Information

### 11.1 LMZ35003 Operation

The LMZ35003 can operate over a wide input voltage range of 7 V to 50 V and produce output voltages from 2.5 V to 15 V. The performance of the device varies over this wide operating range, and there are some important considerations when operated near the boundary limits. This section offers guidance in selecting the optimum components depending on the application and operating conditions.

The user must select three primary parameters when designing with the LMZ35003.

- Output Voltage

- UVLO Threshold

- Switching Frequency

The adjustment of each of these parameters can be made using just one or two resistors. Figure 25 below shows a typical LMZ35003 schematic with the key parameter-setting resistors labeled.

Figure 25. LMZ35003 Typical Schematic

### 11.2 Adjusting the Output Voltage

The LMZ35003 is designed to provide output voltages from 2.5V to 15V. The output voltage is determined by the value of  $R_{\text{SET}}$ , which must be connected between the VOUT node and the VADJ pin (Pin 36). For output voltages greater than 5.0V, improved operating performance can be obtained by increasing the operating frequency. This adjustment requires the addition of  $R_{\text{RT}}$  between RT/CLK (Pin 31) and AGND (Pin 30). See the Switching Frequency section for more details. Table 4 gives the standard external  $R_{\text{SET}}$  resistor for a number of common bus voltages and also includes the recommended  $R_{\text{RT}}$  resistor for output voltages above 5.0V.

Table 4. Standard R<sub>SET</sub> Resistor Values for Common Output Voltages

|                       |      | OUTPUT VOLTAGE V <sub>OUT</sub> (V) |      |      |     |     |  |  |  |

|-----------------------|------|-------------------------------------|------|------|-----|-----|--|--|--|

| RESISTORS             | 2.5  | 15.0                                |      |      |     |     |  |  |  |

| R <sub>SET</sub> (kΩ) | 21.5 | 31.6                                | 52.3 | 90.9 | 140 | 178 |  |  |  |

| R <sub>RT</sub> (kΩ)  | open | open open 1100 549 267              |      |      |     |     |  |  |  |

For other output voltages the value of  $R_{SET}$  can be calculated using the following formula, or simply selected from the range of values given in Table 5.

$$R_{SET} = 10 \times \left(\frac{V_{OUT}}{0.798} - 1\right) (k\Omega)$$

(1)

Table 5. Standard R<sub>SET</sub> and R<sub>RT</sub> Resistor Values

|                      |                       |                      | 3L1                   | 101                  |                       |                   |                       |

|----------------------|-----------------------|----------------------|-----------------------|----------------------|-----------------------|-------------------|-----------------------|

| V <sub>OUT</sub> (V) | R <sub>SET</sub> (kΩ) | R <sub>RT</sub> (kΩ) | f <sub>SW</sub> (kHz) | V <sub>OUT</sub> (V) | R <sub>SET</sub> (kΩ) | $R_{RT}(k\Omega)$ | f <sub>SW</sub> (kHz) |

| 2.5                  | 21.5                  | open                 | 400                   | 9.0                  | 102                   | 365               | 700                   |

| 3.0                  | 27.4                  | open                 | 400                   | 9.5                  | 110                   | 365               | 700                   |

| 3.3                  | 31.6                  | open                 | 400                   | 10.0                 | 115                   | 365               | 700                   |

| 3.5                  | 34.0                  | open                 | 400                   | 10.5                 | 121                   | 267               | 800                   |

| 4.0                  | 40.2                  | open                 | 400                   | 11.0                 | 127                   | 267               | 800                   |

| 4.5                  | 46.4                  | open                 | 400                   | 11.5                 | 133                   | 267               | 800                   |

| 5.0                  | 52.3                  | 1100                 | 500                   | 12.0                 | 140                   | 267               | 800                   |

| 5.5                  | 48.7                  | 1100                 | 500                   | 12.5                 | 147                   | 215               | 900                   |

| 6.0                  | 64.9                  | 1100                 | 500                   | 13.0                 | 154                   | 215               | 900                   |

| 6.5                  | 71.5                  | 1100                 | 500                   | 13.5                 | 158                   | 215               | 900                   |

| 7.0                  | 78.7                  | 549                  | 600                   | 14.0                 | 165                   | 178               | 1000                  |

| 7.5                  | 84.5                  | 549                  | 600                   | 14.5                 | 174                   | 178               | 1000                  |

| 8.0                  | 90.9                  | 549                  | 600                   | 15.0                 | 178                   | 178               | 1000                  |

| 8.5                  | 97.6                  | 365                  | 700                   |                      |                       |                   |                       |

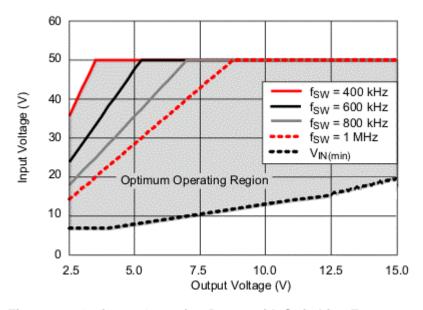

#### 11.3 Input Voltage

The LMZ35003 operates over the input voltage range of 7 V to 50 V. For reliable start-up and operation at light loads, the minimum input voltage depends on the output voltage. For output voltages  $\leq$  12V, the minimum input voltage is 7V or (VOUT + 3V), whichever is greater. For output voltages > 12V, the minimum input voltage is (1.33 x VOUT).

The maximum input voltage is (15 x VOUT) or 50 V, whichever is less.

While the device can safely handle input surge voltages up to 65 V, sustained operation at input voltages above 50 V is not recommended.

See the Undervoltage Lockout (UVLO) Threshold section of this datasheet for more information.

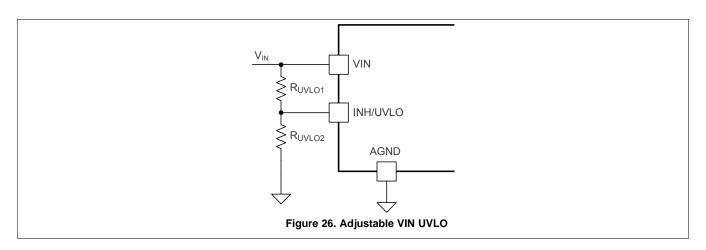

### 11.4 Undervoltage Lockout (UVLO) Threshold

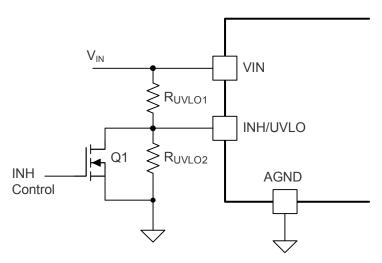

At turn-on, the  $V_{ON}$  UVLO threshold determines the input voltage level where the device begins power conversion. During the power-down sequence, the  $V_{OFF}$  UVLO threshold determines the input voltage where power conversion ceases. The turn-on and turn-off thresholds are set by two resistors,  $R_{UVLO1}$  and  $R_{UVLO2}$  as shown in Figure 26.

The  $V_{ON}$  UVLO threshold must be set to at least (VOUT + 3 V) or 7 V whichever is greater to insure proper startup and reduce current surges on the host input supply as the voltage rises. If possible, it is recommended to set the UVLO threshold to appproximantely 80 to 85% of the minimum expected input voltage.

Use Equation 2 and Equation 3 to calculate the values of  $R_{UVLO1}$  and  $R_{UVLO2}$ .  $V_{ON}$  is the voltage threshold during power-up when the input voltage is rising.  $V_{OFF}$  is the voltage threshold during power-down when the input voltage is decreasing.  $V_{OFF}$  should be selected to be at least 500mV less than  $V_{ON}$ . Table 6 lists standard resistor values for  $R_{UVLO1}$  and  $R_{UVLO2}$  for adjusting the  $V_{ON}$  UVLO threshold for several input voltages.

$$R_{UVLO1} = \frac{(V_{ON} - V_{OFF})}{2.9 \times 10^{-3}} (k\Omega)$$

$$R_{UVLO2} = \frac{1.25}{\left(\frac{(V_{ON} - 1.25)}{R_{UVLO1}}\right) + 0.9 \times 10^{-3}} (k\Omega)$$

(2)

Table 6. Standard Resistor Values to set V<sub>ON</sub> UVLO Threshold

| V <sub>ON</sub> THRESHOLD (V)   | 6.5  | 10.0 | 15.0 | 20.0 | 25.0 | 30.0 | 35.0 | 40.0 | 45.0 |

|---------------------------------|------|------|------|------|------|------|------|------|------|

| $R_{UVLO1}$ ( $k\Omega$ )       | 174  | 174  | 174  | 174  | 174  | 174  | 174  | 174  | 174  |

| $R_{UVLO2}\left(k\Omega\right)$ | 40.2 | 24.3 | 15.8 | 11.5 | 9.09 | 7.50 | 6.34 | 5.62 | 4.99 |

#### 11.5 Power Good (PWRGD)

The PWRGD pin is an open drain output. Once the output voltage is between 94% and 106% of the set voltage, the PWRGD pin pull-down is released and the pin floats. The recommended pull-up resistor value is between 10  $k\Omega$  and 100  $k\Omega$  to a voltage source that is 5.5 V or less. The PWRGD pin is in a defined state once VIN is greater than 1.0 V, but with reduced current sinking capability. The PWRGD pin achieves full current sinking capability once the VIN pin is above 4.5V. The PWRGD pin is pulled low when the output voltage is lower than 91% or greater than 109% of the nominal set voltage. Also, the PWRGD pin is pulled low if the input UVLO or thermal shutdown is asserted, the INH pin is pulled low, or the SS/TR pin is below 1.4 V.

### 11.6 Switching Frequency

Nominal switching frequency of the LMZ35003 is set from the factory at 400 kHz. This switching frequency is optimum for output voltages below 5.0 V. For output voltages 5.0V and above, better operating performance can be obtained raising the operating frequency. This is easily done by adding a resistor,  $R_{RT}$  in , from the RT/CLK pin (Pin 31) to the AGND pin (Pin 30). Raising the operating frequency reduces output voltage ripple, lowers the load current threshold where pulse skipping begins, and improves transient response.

The recommended switching frequency for all output voltages is listed in Table 5.

For the maximum recommended output voltage value of 15 V, the switching frequency computes to 1000 kHz or 1 MHz. Operation above 1 MHz is not recommended. Use Table 7 below to select the value of the timing resistor for the given values of switching frequencies.

Table 7. Standard Resistor Values to set the Switching Frequency

| f <sub>SW</sub> (kHz) | 400  | 500  | 600 | 700 | 800 | 900 | 1000 |

|-----------------------|------|------|-----|-----|-----|-----|------|

| $R_{RT}(k\Omega)$     | OPEN | 1100 | 549 | 365 | 267 | 215 | 178  |

It is also possible to synchronize the switching frequency to an external clock signal. See the Synchronization (CLK) section for further details.

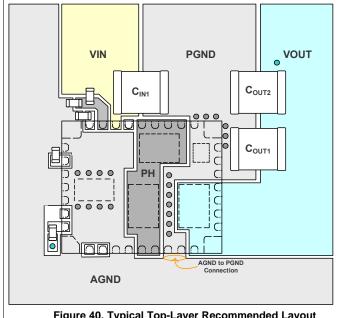

While it is possible to set the operating frequency higher than 400 kHz when using the device at output voltages of 5 V or less, minimum duty cycle and pulse skipping issues restrict the maximum recommended input voltage under these conditions. The recommended operating conditions for the LMZ35003 can be summarized by Figure 27. The graph shows the maximum input voltage vs. output voltage restriction for several operating frequencies. The lower boundary of the graph shows the minimum input voltage as a function of the output voltage.

Figure 27. Optimum Operating Range with Switching Frequency

# 11.7 Application Schematics

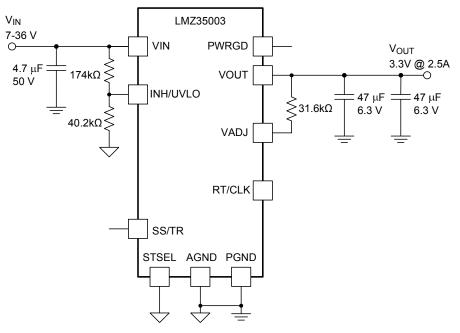

Figure 28. Typical Schematic VIN = 7 V to 36 V, VOUT = 3.3 V

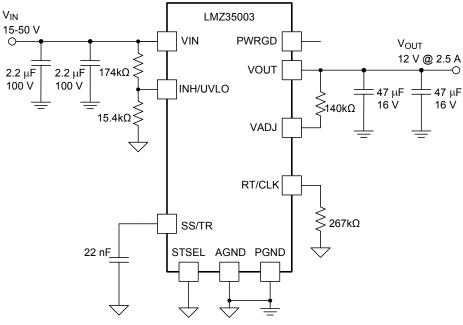

Figure 29. Typical Schematic VIN = 15 V to 50 V, VOUT = 12 V

Copyright © 2013–2018, Texas Instruments Incorporated

# **Application Schematics (continued)**

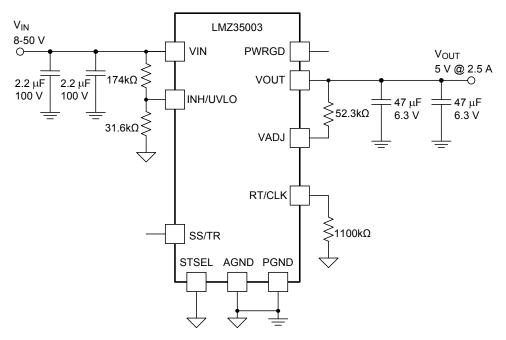

Figure 30. Typical Schematic VIN = 8 V to 50 V, VOUT = 5 V

Submit Documentation Feedback

### 11.8 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LMZ35003 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- · Run thermal simulations to understand board thermal performance

- · Export customized schematic and layout into popular CAD formats

- · Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

### 11.9 Power-Up Characteristics

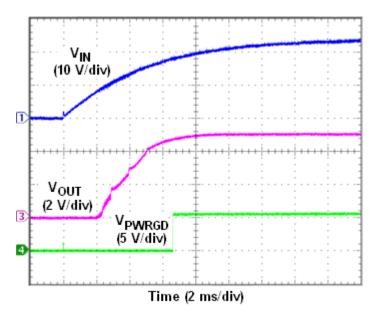

When configured as shown in the front page schematic, the LMZ35003 produces a regulated output voltage following the application of a valid input voltage. During the power-up, internal soft-start circuitry slows the rate that the output voltage rises, thereby limiting the amount of in-rush current that can be drawn from the input source. The soft-start circuitry introduces a short time delay from the point that a valid input voltage is recognized. Figure 31 shows the start-up waveforms for a LMZ35003, operating from a 24-V input and the output voltage adjusted to 5 V. The waveform were measured with a 2-A constant current load.

Figure 31. Start-Up Sequence

Product Folder Links: *LMZ*35003

Copyright © 2013-2018, Texas Instruments Incorporated

### 11.10 Output On/Off Inhibit (INH)

The INH pin provides electrical on/off control of the device. Once the INH pin voltage exceeds the threshold voltage, the device starts operation. If the INH pin voltage is pulled below the threshold voltage, the regulator stops switching and enters low quiescent current state.

The INH pin has an internal pull-up current source, allowing the user to float the INH pin for enabling the device. If an application requires controlling the INH pin, use an open drain/collector device, or a suitable logic gate to interface with the pin.

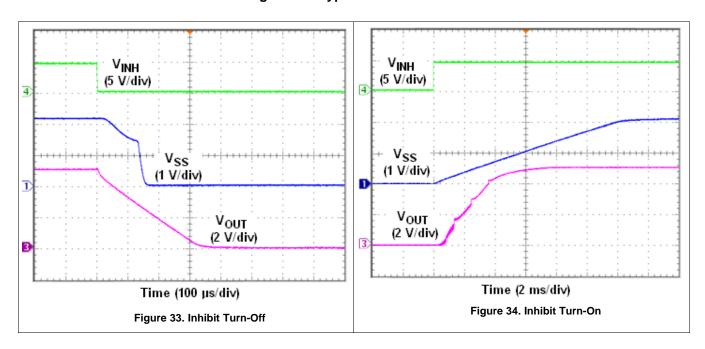

Figure 32 shows the typical application of the inhibit function. The Inhibit control has its own internal pull-up to VIN potential. An open-collector or open-drain device is recommended to control this input.

Turning Q1 on applies a low voltage to the inhibit control (INH) pin and disables the output of the supply, shown in Figure 33. If Q1 is turned off, the supply executes a soft-start power-up sequence, as shown in Figure 34. A regulated output voltage is produced within 5 ms. The waveforms were measured with a 2-A constant current load.

Figure 32. Typical Inhibit Control

Submit Documentation Feedback

Copyright © 2013–2018, Texas Instruments Incorporated

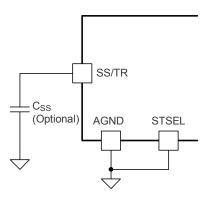

#### 11.11 Slow Start (SS/TR)

For outputs voltages of 5V or less, the slow start capacitance built into the LMZ35003 is sufficient to provide for a turn-on ramp rate that does not induce large surge currents while charging the output capacitors. Connecting the STSEL pin (Pin 29) to AGND while leaving SS pin (Pin 28) open enables the internal SS capacitor with a slow start interval of approximately 5 ms. For output voltages greater than 5V, additional slow start capacitance is recommended. For 12V to 15V output voltages, a 22nF capacitor should be connected between the SS/TR pin (Pin 28) and AGND, while connecting the STSEL pin (Pin 29) to AGND as well. Figure 35 shows an additional SS capacitor connected to the SS pin and the STSEL pin connected to AGND. See Table 8 below for SS capacitor values and timing interval.

Figure 35. Slow Start Capacitor (C<sub>SS</sub>) and STSEL Connection

**Table 8. Slow Start Capacitor Values and Slow Start Time**

| C <sub>SS</sub> (nF) | open | 4.7 | 10 | 15 | 22 |

|----------------------|------|-----|----|----|----|

| SS Time (msec)       | 5    | 7   | 10 | 13 | 17 |

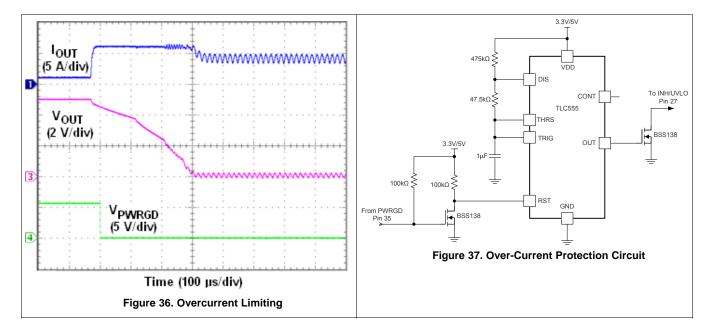

#### 11.12 Overcurrent Protection

For protection against load faults, the LMZ35003 incorporates cycle-by-cycle current limiting. During an overcurrent condition the output current is limited and the output voltage is reduced, as shown in Figure 36. As the output voltage drops more than 8% below the set point, the PWRGD signal is pulled low. If the output voltage drops more than 25%, the switching frequency is reduced to reduce power dissipation within the device. When the overcurrent condition is removed, the output voltage returns to the established voltage.

The LMZ35003 is not designed to endure a sustained short circuit condition. The use of an output fuse, voltage supervisor circuit, or other overcurrent protection circuit is recommended. A recommended overcurrent protection circuit is shown in Figure 37. This circuit uses the PWRGD signal as an indication of an overcurrent condition. As PWRGD remains low, the 555 timer operates as a low frequency oscillator, driving the INH/UVLO pin low for approximately 400ms, halting the power conversion of the device. After the inhibit interval, the INH/UVLO pin is released and the LMZ35003 restarts. If the overcurrent condition is removed, the PWRGD signal goes high, resetting the oscillator and power conversion resumes, otherwise the inhibit cycle repeats.

Submit Documentation Feedback

Copyright © 2013–2018, Texas Instruments Incorporated

#### 11.13 Light-Load Behavior

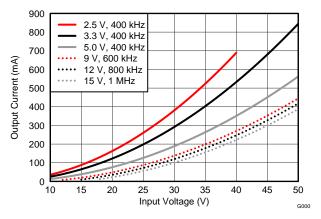

The LMZ35003 is a non-synchronous converter. One of the characteristics of a non-synchronous converter is that as the load current on the output is decreased, a point is reached where the energy delivered by a single switching pulse is more than the load can absorb. This causes the output voltage to rise slightly. This rise in output voltage is sensed by the feedback loop and the device responds by skipping one or more switching cycles until the output voltages falls back to the set point. At very light loads or no load, many switching cycles are skipped. The observed effect during this pulse skipping mode of operation is an increase in the peak to peak ripple voltage, and a decrease in the ripple frequency. The load current where pulse skipping begins is a function of the input voltage, the output voltage, and the switching frequency. A plot of the pulse skipping threshold current as a function of input voltage is given in Figure 38 for a number of popular output voltage and switching frequency combinations.

Figure 38. Pulse Skipping Threshold

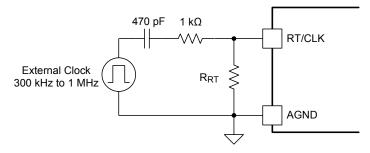

# 11.14 Synchronization (CLK)

An internal phase locked loop (PLL) allows synchronization between 400 kHz and 1 MHz, and to easily switch from RT mode to CLK mode. To implement the synchronization feature, connect a square wave clock signal to the RT/CLK pin with a duty cycle between 20% to 80%. The clock signal amplitude must transition lower than 0.8 V and higher than 2.0 V. The start of the switching cycle is synchronized to the falling edge of RT/CLK pin. In applications where both RT mode and CLK mode are needed, the device can be configured as shown in Figure 39.

Before the external clock is present, the device works in RT mode where the switching frequency is set by the  $R_{RT}$  resistor. When the external clock is present, the CLK mode overrides the RT mode. The first time the CLK pin is pulled above the RT/CLK high threshold (2.0 V), the device switches from RT mode to CLK mode and the RT/CLK pin becomes high impedance as the PLL starts to lock onto the frequency of the external clock. It is not recommended to switch from CLK mode back to RT mode because the internal switching frequency drops to 100 kHz first before returning to the switching frequency set by the  $R_{RT}$  resistor .

Figure 39. CLK/RT Configuration

#### 11.15 Thermal Shutdown

The internal thermal shutdown circuitry forces the device to stop switching if the junction temperature exceeds 180°C typically. The device reinitiates the power up sequence when the junction temperature drops below 165°C typically.

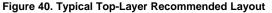

# 11.16 Layout Considerations

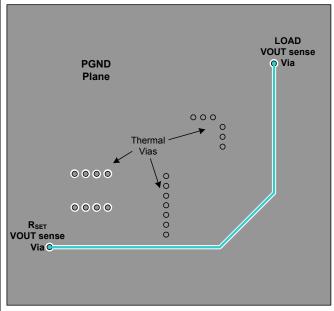

To achieve optimal electrical and thermal performance, an optimized PCB layout is required. Figure 40 and Figure 41 show two layers of a typical PCB layout. Some considerations for an optimized layout are:

- Use large copper areas for power planes (VIN, VOUT, and PGND) to minimize conduction loss and thermal stress.

- Place ceramic input and output capacitors close to the module pins to minimize high frequency noise.

- Locate additional output capacitors between the ceramic capacitor and the load.

- Place a dedicated AGND copper area beneath the LMZ35003.

- Isolate the PH copper area from the VOUT copper area using the PGND copper area.

- Connect the AGND and PGND copper area at one point; at pins 8 & 9.

- Place R<sub>SET</sub>, R<sub>RT</sub>, and C<sub>SS</sub> as close as possible to their respective pins.

- Use multiple vias to connect the power planes to internal layers.

- Use a dedicated sense line to connect R<sub>SET</sub> to VOUT near the load for best regulation.

Figure 41. Typical PGND-Layer Recommended Layout

Submit Documentation Feedback

#### 11.17 EMI

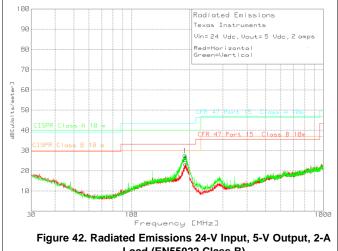

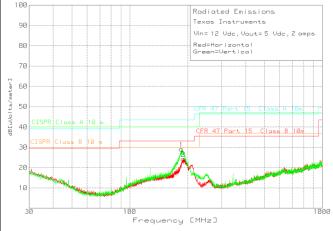

The LMZ35003 is compliant with EN55022 Class B radiated emissions. Figure 42 and Figure 43 show typical examples of radiated emissions plots for the LMZ35003 operating from 24 V and 12 V respectively. Both graphs include the plots of the antenna in the horizontal and vertical positions.

Load (EN55022 Class B)

Figure 43. Radiated Emissions 12-V Input, 5-V Output, 2-A Load (EN55022 Class B)

# 12 Revision History

| Changes from Revision A (June 2017) to Revision B                                                                 | Page |

|-------------------------------------------------------------------------------------------------------------------|------|

| Added WEBENCH® design links for the LMZ35003                                                                      | 1    |

| <ul> <li>Increased the peak reflow temperature and maximum number of reflows to JEDI manufacturability</li> </ul> | ·    |

| Added Device and Documentation Support section                                                                    | 27   |

| Added Mechanical, Packaging, and Orderable Information section                                                    |      |

| Changes from Original (July 2013) to Revision A                                                                   | Page |

| Deleted graphic above title                                                                                       | 1    |

| Added peak reflow and maximum number of reflows information                                                       | 2    |

### 13 Device and Documentation Support

### 13.1 Device Support

#### 13.1.1 Development Support

#### 13.1.1.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LMZ35003 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- · Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

### 13.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 13.3 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 13.4 Trademarks

E2E is a trademark of Texas Instruments.

WEBENCH is a registered trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 13.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 13.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 14 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

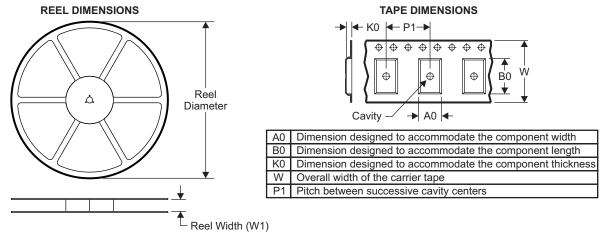

### 14.1 Tape and Reel Information

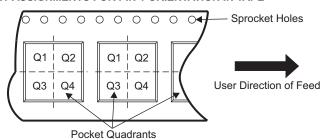

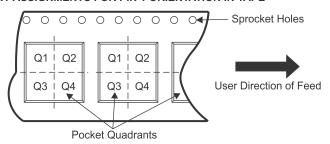

#### **QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

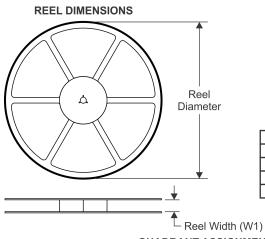

| Device       | Package<br>Type | Package<br>Drawing | Pins | SPQ | Reel<br>Diameter<br>(mm) | Reel<br>Width W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|------|-----|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMZ35003RKGR | B1QFN           | RKG                | 41   | 500 | 330.0                    | 24.4                     | 9.35       | 11.35      | 3.1        | 16.0       | 24.0      | Q1               |

| LMZ35003RKGT | B1QFN           | RKG                | 41   | 250 | 330.0                    | 24.4                     | 9.35       | 11.35      | 3.1        | 16.0       | 24.0      | Q1               |

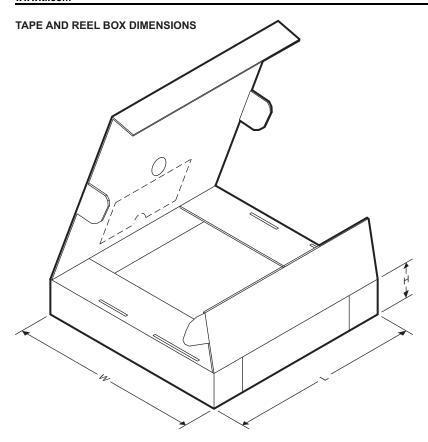

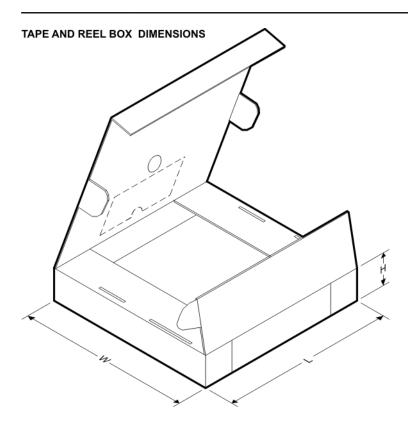

| Device       | Package Type | Package Drawing | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|-----|-------------|------------|-------------|

| LMZ35003RKGR | B1QFN        | RKG             | 41   | 500 | 383.0       | 353.0      | 58.0        |

| LMZ35003RKGT | B1QFN        | RKG             | 41   | 250 | 383.0       | 353.0      | 58.0        |

# PACKAGE OPTION ADDENDUM

4-Jun-2020

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan               | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|------------------------|------------------|---------------------|--------------|----------------------|---------|

| LMZ35003RKGR     | ACTIVE | B1QFN        | RKG                | 41   | 500            | RoHS Exempt<br>& Green | NIPDAU           | Level-3-250C-168 HR | -40 to 85    | (54260, LMZ35003)    | Samples |

| LMZ35003RKGT     | ACTIVE | B1QFN        | RKG                | 41   | 250            | RoHS Exempt<br>& Green | NIPDAU           | Level-3-250C-168 HR | -40 to 85    | (54260, LMZ35003)    | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

4-Jun-2020

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 10-Mar-2021

# TAPE AND REEL INFORMATION

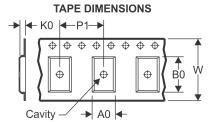

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|-----|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMZ35003RKGR | B1QFN           | RKG                | 41 | 500 | 330.0                    | 24.4                     | 9.35       | 11.35      | 3.1        | 16.0       | 24.0      | Q1               |

| LMZ35003RKGT | B1QFN           | RKG                | 41 | 250 | 330.0                    | 24.4                     | 9.35       | 11.35      | 3.1        | 16.0       | 24.0      | Q1               |

www.ti.com 10-Mar-2021

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|-----|-------------|------------|-------------|

| LMZ35003RKGR | B1QFN        | RKG             | 41   | 500 | 383.0       | 353.0      | 58.0        |

| LMZ35003RKGT | B1QFN        | RKG             | 41   | 250 | 383.0       | 353.0      | 58.0        |

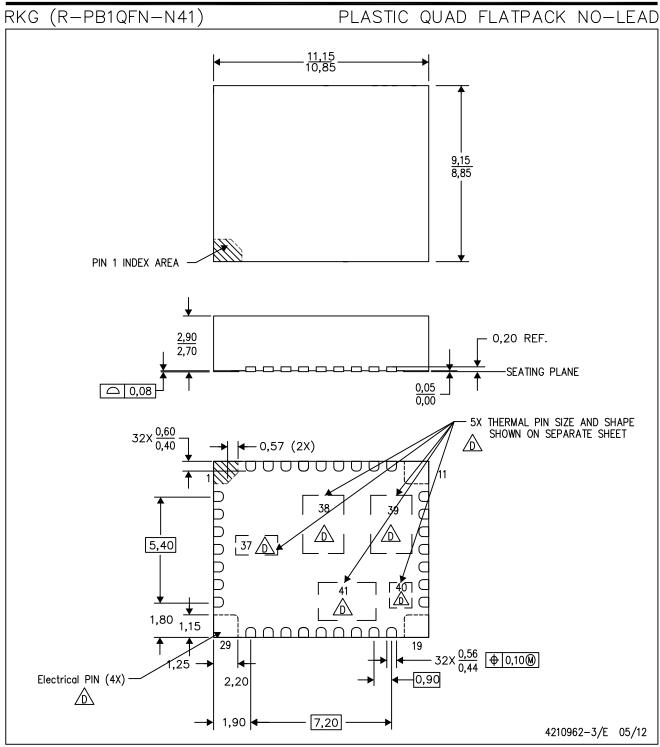

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Quad Flatpack, No-leads (QFN) package configuration.

- 1 The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- $\sqrt{F}$ .\ The package thermal performance may be enhanced by bonding the thermal pad to an external thermal plane.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated